All Products

-

Integrated Circuits (ICs)

- Integrated Circuits (ICs)

- AC to DC Converter ICs

- Active Filters

- ADC

- AFE

- Analog Multipliers & Dividers

- Analog Switches & Multiplexers ICs

- Application Specific Microcontrollers

- Application Specific Timer

- Audio Amplifiers

- Audio Special Purpose

- Battery Chargers ICs

- Battery Management ICs

- Buffers & Transceivers

- Capacitive Sensors

- Clock Buffers & Drivers

- Clock Generators

- CODECs Interface ICs

- Comparators

- Configuration Proms for FPGAs

- Controllers Interface ICs

- Converting Interface ICs

- Counters & Dividers

- CPLDs

- Current Regulator IC

- DAC

- DC DC Voltage Regulators

- DC to DC converter

- DDS

- Delay Lines Timing ICs

- Digital Potentiometers

- Display Drivers ICs

- Drivers Interface ICs

- DSP

- Embedded ICs Modules

- Energy Metering ICs

- FIFOs Memory

- Flip Flops

- FPGAs

- FPGAs with Microcontrollers

- Full & Half-Bridge Drivers ICs

- Gate Drivers ICs

- Gates & Inverters

- Hot Swap Controllers

- I/O Expanders

- IC Batteries

- Ideal Diode controller

- Instrumentational OP Amps

- Interface ICs Modules

- Laser Driver ICs

- Latches

- LED Driver ICs

- Lighting Controllers

- Linear Comparators

- Linear Regulator Controllers

- Linear Voltage Regulators

- Memory

- Memory Batteries

- Memory Controllers

- Microcontrollers

- Microprocessors

- Modems ICs & Modules

- Motor Drivers

- Multi-Functional Gates & Inverters

- Multivibrators

- Multivibrators

- PFC PMICs

- PLDs

- PoE Controllers

- Power Supply Control ICs

- Power Switches ICs

- Programmable Timers & Oscillators

- RMS to DC Converters

- RTCs

- Sensor & Detector Interface ICs

- Serializers & Deserializers

- Shift Registers

- Signal Buffers

- Signal Switches & Multiplexers

- Signal Terminators

- SoC

- Special Purpose ADCs/DACs

- Special Purpose Amplifiers

- Special Purpose Analog Switches

- Specialized ICs

- Specialized Interface ICs

- Specialized Power Management ICs

- Specialized Voltage Regulators

- Specialty Logic ICs

- Switching Voltage Regulators

- Telecom Interface ICs

- Thermal Management

- Touch Screen Controllers

- UARTs

- Universal Bus Functions

- V/F & F/V Converters

- Video Amps & Modules

- Video Processing Linear ICs

- Voice Record and Playback

- Voltage Reference

- Voltage Supervisors

- Voltage Translators & Level Shifters

-

Connectors

- Connectors

- ARINC Connectors

- Backplane Connector Contacts

- Backplane Connectors Accessories

- Backplane Connectors Housings

- Backshells and Cable Clamps

- Banana Tip Adapters

- Banana Tip Binding Posts

- Banana Tip Connectors Accessories

- Banana Tip Jacks

- Barrel Accessories

- Barrel Adapters

- Barrel Audio Connectors

- Barrel Connectors

- Barrel Power Connectors

- Barrier Terminal Blocks

- Between Series Adapters

- Blade Type Power Connectors

- Blade Type Power Connectors

- Blade Type Power Connectors Accessories

- Blade Type Power Connectors Housings

- Board In Connectors

- Board to Board Connectors

- Card Edge Adapters

- Card Edge Connectors Accessories

- Card Edge Connectors Housings

- Card Edge Contacts

- Centronics Connectors

- Circular Adapters

- Circular Connectors

- Circular Connectors Accessories

- Circular Connectors Housings

- Circular Contacts

- Coaxial Connectors

- Coaxial Connectors Accessories

- D-Sub Adapters

- D-Sub Connector Housings

- D-Sub Connector Terminators

- D-Sub Connectors

- D-Sub Connectors Accessories

- D-Sub Contacts

- D-Sub Hoods

- D-Sub Jackscrews

- DIN 41612 Connectors

- Din Rail Terminal Blocks

- Edgeboard Connectors

- Faceplates & Frames

- Fiber Optic Adapters

- Fiber Optic Connectors

- Fiber Optic Connectors Accessories

- Fiber Optic Connectors Housings

- Flat Flexible Connector Housings

- Flat Flexible Connectors

- Flat Flexible Connectors Accessories

- Flat Flexible Contacts

- Foil Connectors

- Hard Metric Connector

- Headers & Male Pins

- Heavy Duty Connectors Accessories

- Heavy Duty Connectors Assemblies

- Heavy Duty Connectors Frames

- Heavy Duty Connectors Housings

- Heavy Duty Connectors Modules

- Heavy Duty Contacts

- IC Adapters

- IC and Component Sockets

- IC Sockets Accessories

- Inline Memory Module Sockets

- Interface Modules Terminal Blocks

- Keystone Accessories

- Keystone Inserts

- Knife Connectors

- Leadframe Contacts

- LGH Connectors

- Magnetic Wire Terminals

- Magnetics Modular Jacks

- Memory Card Adapters

- Memory Card Sockets

- Memory Connectors Accessories

- Modular Adapters

- Modular Connectors Accessories

- Modular Jacks

- Modular Plug Housings

- Modular Plugs

- Multi Purpose Contacts

- Panel Mount Connectors

- Panel Mount Terminal Blocks

- PC Pin Terminals

- Photovoltaic Connectors

- Photovoltaic Connectors Accessories

- Photovoltaic Contacts

- Pluggable Connectors

- Pluggable Connectors Accessories

- Pluggable Terminal Blocks

- Power Distribution Terminal Blocks

- Power Entry Connectors Accessories

- Power Entry Connectors Modules

- Quick-Connect & Quick-Disconnect Connectors

- Rectangular Connectors

- Rectangular Connectors Accessories

- Rectangular Connectors Adapters

- Rectangular Connectors Arrays

- Rectangular Connectors Headers

- Rectangular Connectors Housings

- Rectangular Contact Inserts

- Rectangular Terminals

- RF Adapters

- RF Contacts

- RF Terminators

- Ring Terminals

- Screw Connectors

- Shunts & Jumpers

- Socket Terminals

- Solder Lug Connectors

- Spade Connectors

- Specialized Backplane Connectors

- Specialized Connectors

- Specialized Terminal Blocks

- Spring Loaded Contacts

- Spring Loaded Rectangular Connectors

- SSL Connectors

- SSL Connectors Accessories

- SSL Contacts

- Terminal Block Adapters

- Terminal Blocks - Contacts

- Terminal Blocks Accessories

- Terminal Jumpers

- Terminal Junction Systems

- Terminal Marker Strips

- Terminal Strips and Turret Boards

- Terminal Wire Ferrules

- Terminals Accessories

- Terminals Adapters

- Terminals Housings

- Transistor Sockets

- Turret Connectors

- Video Adapters

- Video Connector Accessories

- Video Connectors

- Wire Pin Connectors

- Wire Splice Connectors

- Wire-to-Board Connectors

- Wire-to-Board Terminal Blocks

- Wiring Blocks Accessories

- Wiring Modular Connectors

-

Discrete Semiconductors

- Discrete Semiconductors

- Arrays BJT Transistors

- BJT Transistors Arrays

- Bridge Rectifiers

- DIACs and SIDACs

- IGBTs Modules

- IGBTs Transistors Arrays

- JFETs Transistors

- MOSFETs Transistors Arrays

- Power Driver Modules

- Pre-Biased BJT Transistors

- Programmable Unijunction Transistors

- Rectifier Diode Array

- RF BJT Transistors

- RF Diodes

- RF MOSFETs Transistors

- SCRs Thyristors

- Single BJT Transistors

- Single IGBTs

- Single IGBTs

- Single MOSFETs Transistors

- Single-Phase Diode Rectifier

- Specialized Transistors

- Thyristors Modules

- TRIACs Thyristors

- Varactors

- Zener Diode Arrays

- Zener Single Diodes

-

Capacitors

- Capacitors

- Aluminum Electrolytic Capacitors

- Aluminum Polymer Capacitors

- Capacitor Accessories

- Capacitor Networks

- Ceramic Capacitors

- Ceramic Capacitors

- Film Capacitors

- Mica & PTFE Capacitors

- Niobium Oxide Capacitors

- Silicon Capacitors

- Supercapacitors & EDLC

- Tantalum Capacitors

- Tantalum Polymer Capacitors

- Thin Film Capacitors

- Trimmers Variable

-

Sensors

- Sensors

- CdS Cells

- Accelerometers

- Accessories

- Amplifiers

- Analog & Digital Sensor

- Analog & Digital Sensors

- Analog Optical Sensors

- Angle & Linear Position Measuring Sensors

- Camera Modules

- Color Sensors

- Current Sensors

- Distance Measuring Sensors

- Dust Sensors

- Encoders

- Float & Level Sensors

- Flow Sensors

- Force Sensors

- Gas Sensors

- Gyroscopes

- Humidity Sensors

- Image Sensors

- IMUs

- Inclinometers

- IrDA Transceiver Modules

- Junction Blocks

- Logic Optical Sensors

- Logic Photo Detectors

- Logic Photointerrupters

- LVDT Transducers

- Magnetic Compass Sensors Modules

- Magnetic Linear Sensors ICs

- Magnetic Position Sensors Modules

- Magnetic Switches

- Mechanical Temperature Sensors

- Multi Purpose Magnets

- Multifunction

- NTC Thermistors

- Occupancy Sensors

- Optical Motion Sensors

- Optical Sensors Remote Receiver

- Photodiodes

- Photoelectric Sensors

- Phototransistors

- Proximity Sensors

- PTC Thermistors

- RTD

- Sensor Cable Accessories

- Sensor Cable Assemblies

- Sensor Matched Magnets

- Shock Sensors

- Solar Cells

- Solid State Thermostats

- Specialized Sensors

- Strain Gauges

- Thermocouple Temperature Sensors

- Tilt Switch Sensors

- Touch Sensors

- Transducers

- Transistor Optical Sensors

- Ultrasonic Receivers

- UV Sensors

- Vibration Sensors

- Resistors

- Isolators

- Board Mount Poser Supplies

-

RF/IF & RFID

- RF/IF & RFID

- Attenuators

- Balun

- RF Accessories

- RF Amplifiers

- RF Antennas

- RF Boards

- RF Demodulators

- RF Detectors

- RF Directional Coupler

- RF Front End

- RF Misc ICs and Modules

- RF Mixers

- RF Modulators

- RF Multiplexers

- RF Power Controller ICs

- RF Power Dividers

- RF Receivers

- RF Shields

- RF Switches

- RF Transceiver ICs

- RF Transceiver Modules

- RF Transmitter

- RF Transmitters

- RFI & EMI Contacts

- RFI & EMI Materials

- RFID Accessories

- RFID Antennas

- RFID Boards

- RFID ICs

- RFID Reader Modules

- RFID Tags

- Circuit Protection

- Crystals

- Inductors

- Filters

You may place an order without registering to Utmel.

We strongly suggest you sign in before purchasing as you

can track your order in real time.

For your convenience, we accept multiple payment methods in USD, including PayPal, Credit Card, and wire transfer.

RFQ (Request for Quotations)It is recommended to request for quotations to get the latest

prices and inventories about the part.

Our sales will reply to

your request by email within 24 hours.

1. You'll receive an order information email in your inbox.

(Please remember to check the spam folder if you didn't hear from us).

2. Since inventories and prices may fluctuate to some

extent, the sales manager is going to reconfirm the order and let you know if there

are any updates.

Shipping starts at $40, but some countries will exceed $40. For

example (South Africa, Brazil, India, Pakistan, Israel, etc.)

The

basic freight (for package ≤0.5kg or corresponding volume) depends on the time zone and

country.

Currently, our products are shipped through DHL, FedEx, SF, and UPS.

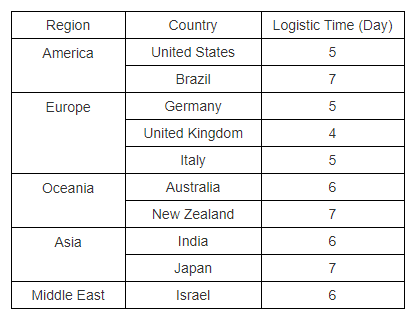

Delivery TimeOnce the goods are shipped, estimated delivery time depends on the shipping methods you chose:

FedEx International, 5-7 business days.

The following are some common countries' logistic time.

| Parameters | |

|---|---|

| Mount | Surface Mount |

| Package / Case | PQFP |

| Number of Pins | 160 |

| Packaging | Bulk |

| Published | 1998 |

| JESD-609 Code | e0 |

| Pbfree Code | no |

| Part Status | Discontinued |

| Moisture Sensitivity Level (MSL) | 3 |

| Number of Terminations | 160 |

| ECCN Code | EAR99 |

| Terminal Finish | Tin/Lead (Sn/Pb) |

| Max Operating Temperature | 70°C |

| Min Operating Temperature | 0°C |

| Additional Feature | YES |

| HTS Code | 8542.39.00.01 |

| Subcategory | Programmable Logic Devices |

| Technology | CMOS |

| Terminal Position | QUAD |

| Terminal Form | GULL WING |

| Peak Reflow Temperature (Cel) | 245 |

| Supply Voltage | 5V |

| Terminal Pitch | 0.65mm |

| Time@Peak Reflow Temperature-Max (s) | NOT SPECIFIED |

| Pin Count | 160 |

| Qualification Status | Not Qualified |

| Supply Voltage-Max (Vsup) | 5.25V |

| Power Supplies | 3.3/55V |

| Temperature Grade | COMMERCIAL |

| Supply Voltage-Min (Vsup) | 4.75V |

| Number of I/O | 124 |

| Clock Frequency | 166.7MHz |

| Propagation Delay | 7.5 ns |

| Programmable Logic Type | EE PLD |

| Number of Gates | 3750 |

| Number of Logic Blocks (LABs) | 12 |

| Output Function | MACROCELL |

| Number of Macro Cells | 192 |

| JTAG BST | YES |

| In-System Programmable | YES |

| Height Seated (Max) | 4.07mm |

| Length | 28mm |

| Width | 28mm |

| RoHS Status | RoHS Compliant |

| Lead Free | Contains Lead |

EPM7192SQC160-7F Overview

In the mobile phone network, there are 192macro cells, which are cells with high-power antennas and towers.The item is packaged with PQFP.It is programmed with 124 I/Os.It is programmed to terminate devices at [0].This electrical part has a terminal position of QUADand is connected to the ground.An electrical supply voltage of 5V is used to power it.This part is in the family [0].It is recommended to package the chip by Bulk.It has 160pins programmed.This device is also capable of displaying [0].In digital circuits, there are 3750gates, which act as a basic building block.Surface Mountis the mounting point of this electronic part.The device has a pinout of [0].This device runs on 3.3/55Vvolts of electricity.A maximum supply voltage (Vsup) of 5.25V is provided.There should be a temperature above 0°Cat the time of operation.Ideally, the operating temperature should be below 70°C.Its basic building block is composed of 12 logic blocks (LABs).Voltage supply (Vsup) should be higher than 4.75V.It should not exceed 166.7MHzin terms of clockfrequency.It is possible to classify programmable logic as EE PLD.

EPM7192SQC160-7F Features

PQFP package

124 I/Os

160 pin count

160 pins

3.3/55V power supplies

12 logic blocks (LABs)

EPM7192SQC160-7F Applications

There are a lot of Altera EPM7192SQC160-7F CPLDs applications.

- Address decoding

- Multiple Clock Source Selection

- State machine design

- Boolean function generators

- Interface bridging

- Software-Driven Hardware Configuration

- Software-driven hardware configuration

- ToR/Aggregation/Core Switch and Router

- Battery operated portable devices

- SFP, QSFP, QSFP-DD, OSFP, Mini-SAS HD Port Management